# Programming and physical design tools for flow-based biochips

#### **Paul Pop**

Technical University of Denmark

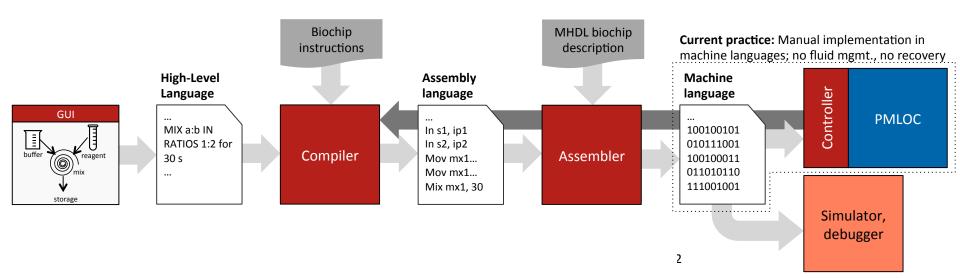

## Programming biochips: vision

High-level language for describing biological protocols

#### **Original protocol**

Add 100 ul of 7X Lysis Buffer (Blue) and mix by inverting the tube 4-6 times.

Proceed to step 3 within 2 minutes.

```

1 ASSAY Glucose START

2 fluid Glucose, Reagent, Sample;

3 fluid a, b, c, d, e;

4 VARResult[5];

5 input Glucose 50;

6 input Reagent;

7 input Sample 30;

8 conflict Sample FOLLOWS Glucose WASH water;

9 a=MIX Glucose AND Reagent IN RATIOS1 : 1

```

Programming tools: compiler, assembler, debugger, simulator

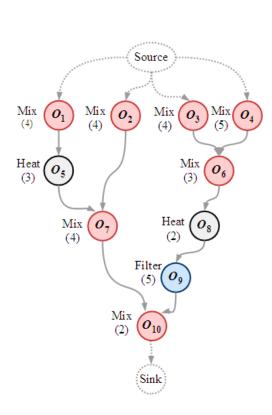

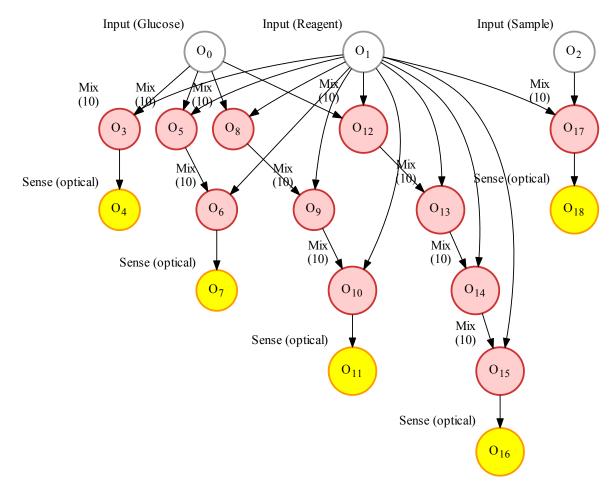

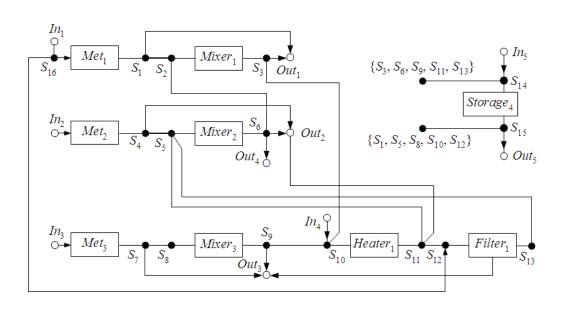

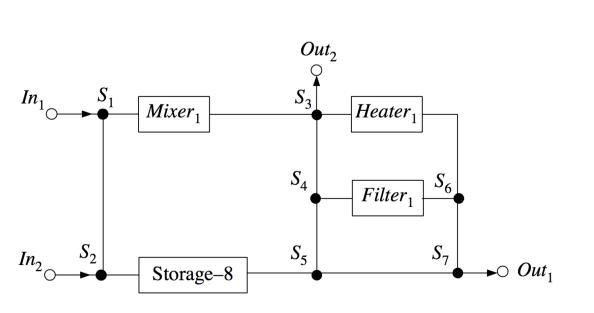

## From HLLs to graph models

We model a biochemical application as a graph

Compiler: translates the protocol written in the HLL into the graph, doing mixing optimization

## The graph model for an enzyme test

Considering a variable mixer module

Considering a 1:1 mixer module; mixing is optimized

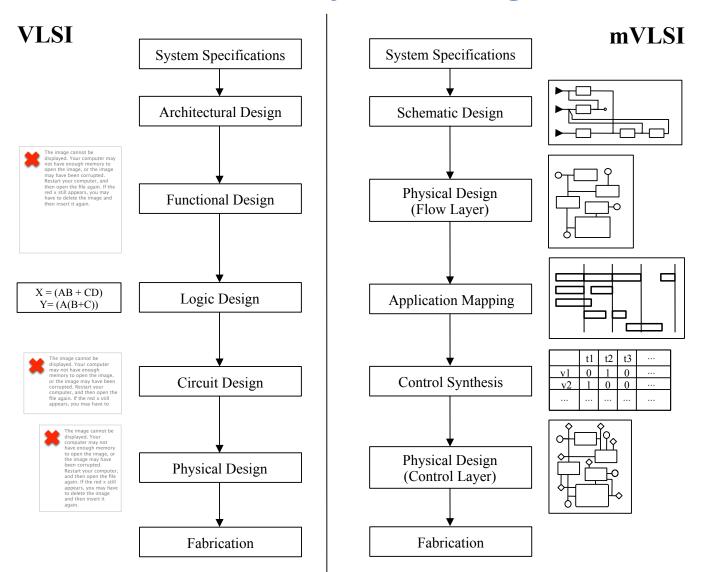

## Physical design: VLSI vs mVLSI

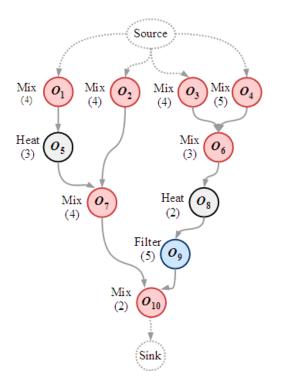

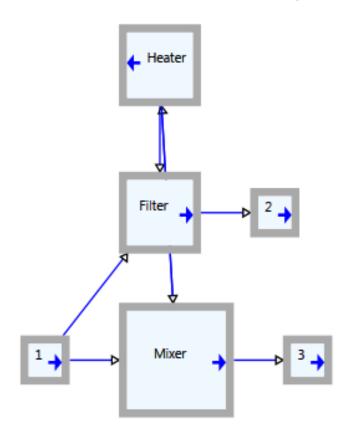

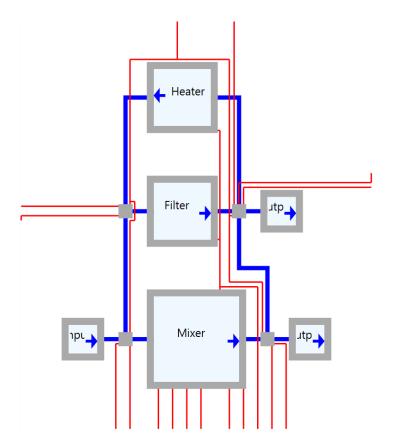

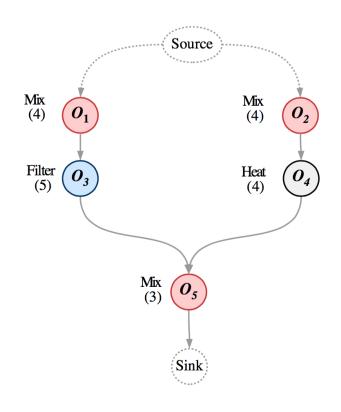

## Allocation and schematic design

How many components, and how to interconnect them?

| Mixer  | 3 |

|--------|---|

| Heater | 2 |

| Filter | 1 |

- Input/ output ports

- Storage units

- Fluidic constraints

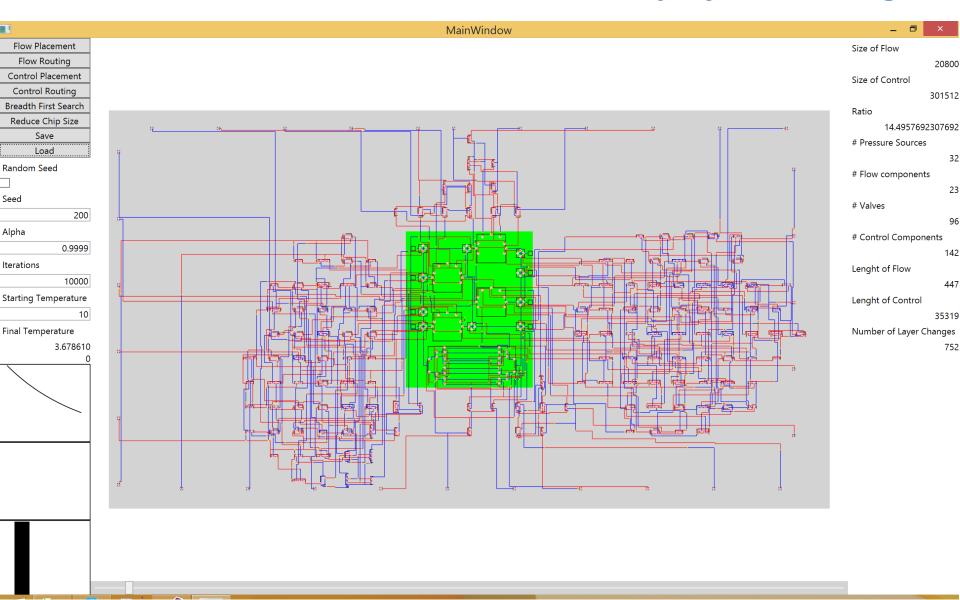

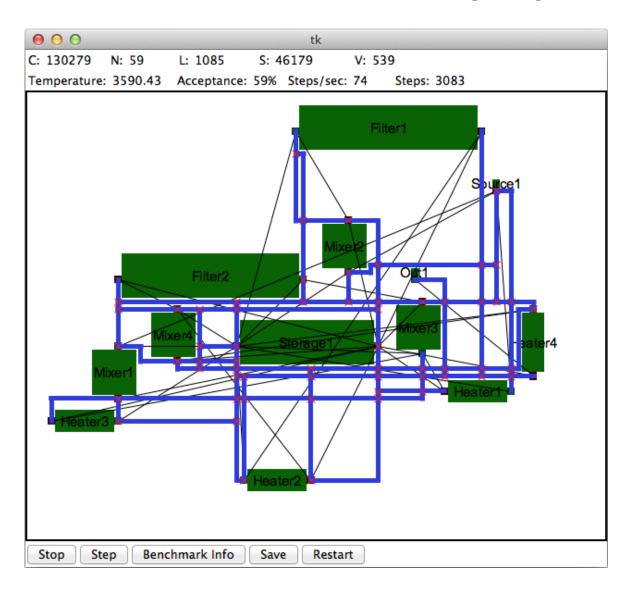

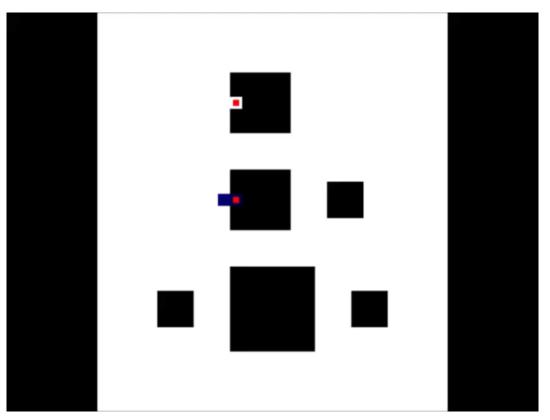

## Flow layer placement

# Flow-channel routing

## Algorithms

Lee, Hadlock, Soukoup

## **Control layer routing**

### Algorithms

- Lee-Steiner: Route from component to nearest air inlet; rip-up and reroute

- PathFinder

Lee-Steiner's algorithm

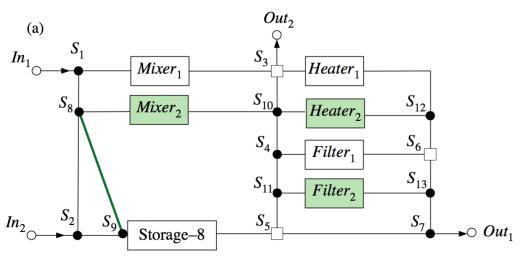

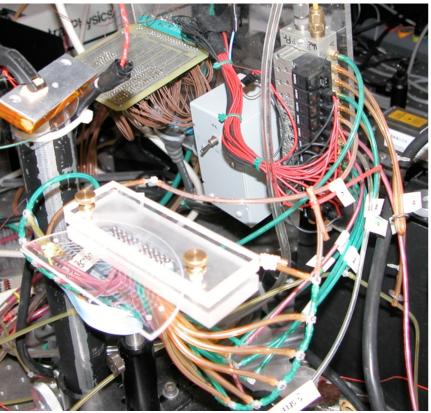

## Design for fault-tolerance: motivation example

Architecture without fault-tolerance

**Application**

## Straightforward vs. optimized redundancy

Straightforward solution: redundancy not optimized; architecture cost: 129

Optimized solution the introduction of redundancy is optimized; architecture cost: 96

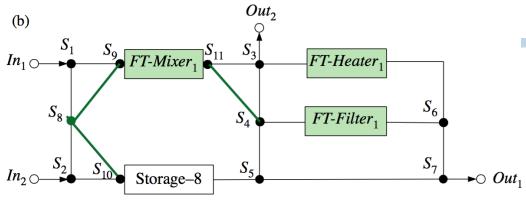

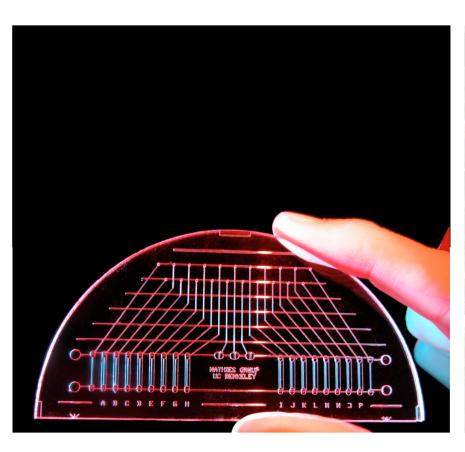

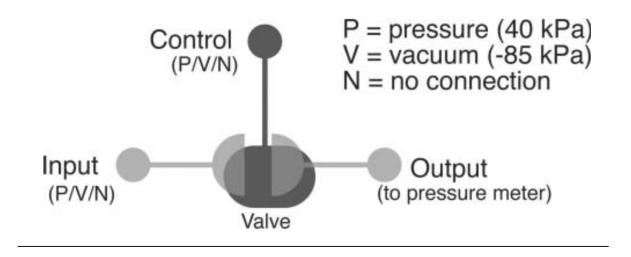

# The need for on-chip control

Slide from Prof. William Grover

## **On-chip control**

| Rule | Maintained<br>at input/kPa | Maintained<br>at control/kPa | Measured<br>at output/kPa |

|------|----------------------------|------------------------------|---------------------------|

| PP   | 40                         | 40                           | 0                         |

| PV   | 40                         | -85                          | 40                        |

| PN   | 40                         | 0                            | 40                        |

| VP   | -85                        | 40                           | 0                         |

| VV   | -85                        | -85                          | -83                       |

| VN   | -85                        | 0                            | 0                         |

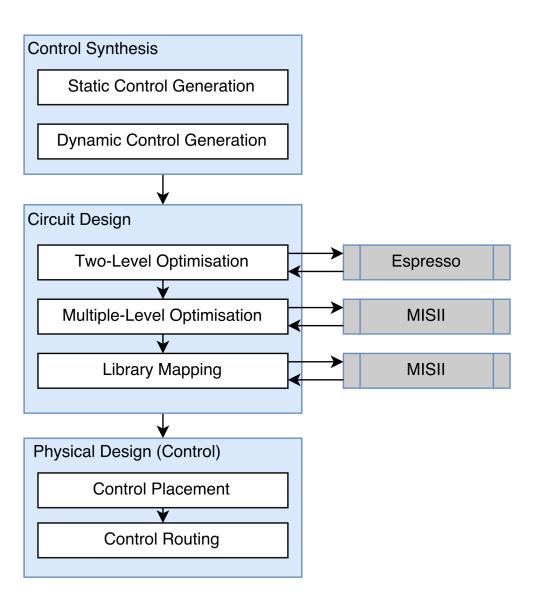

## **Control circuit synthesis...**

## ...and its physical design