#### Design of Mixed-Criticality Applications on Distributed Real-Time Systems

Domițian Tămaș–Selicean

Kongens Lyngby 2014 PhD-2014-329

Technical University of Denmark Department of Applied Mathematics and Computer Science Building 303B, DK-2800 Kongens Lyngby, Denmark Phone +45 45253031, Fax +45 45881399 compute@compute.dtu.dk www.compute.dtu.dk PhD-2014-329

### Summary

A mixed-criticality system implements applications of different safety-criticality levels onto the same platform. In such cases, the certification standards require that applications of different criticality levels are protected so they cannot influence each other. Otherwise, all tasks have to be developed and certified according to the highest criticality level, dramatically increasing the development costs. In this thesis we consider mixed-criticality real-time applications implemented on distributed partitioned architectures.

Partitioned architectures use temporal and spatial separation mechanisms to ensure that applications of different criticality levels do not interfere with each other. With temporal partitioning, each application is allowed to run only within predefined time slots, allocated on each processor. The sequence of time slots for all the applications on a processor are grouped within a Major Frame, which is repeated periodically. Each partition can have its own scheduling policy; we have considered non-preemptive static cyclic scheduling and fixed-priority preemptive scheduling policies. We assume that the communication network implements the TTEthernet protocol, which supports Time-Triggered (TT) messages transmitted based on static schedule tables, Rate Constrained (RC) messages with bounded end-to-end delay, and Best-Effort (BE) messages, for which no timing guarantees are provided. TTEthernet offers spatial separation for mixed-criticality messages through the concept of virtual links, and temporal separation, enforced through schedule tables for TT messages and bandwidth allocation for RC messages.

The objective of this thesis is to develop methods and tools for distributed mixedcriticality real-time systems. At the processor level, we are interested to determine (i) the mapping of tasks to processors, (ii) the assignment of tasks to partitions, (iii) the decomposition of tasks into redundant lower criticality tasks, (iv) the sequence and size of the partition time slots on each processor and (v) the schedule tables, such that all the applications are schedulable and the development and certification costs are minimized. We have proposed Simulated Annealing and Tabu Search metaheuristics to solve these optimization problems. The proposed algorithms have been evaluated using several benchmarks.

At the communication network level, we are interested in the design optimization of TTEthernet networks used to transmit mixed-criticality messages. Given the set of TT and RC messages, and the topology of the network, we are interested to optimize (i) the packing of messages in frames, (ii) the assignment of frames to virtual links, (iii) the routing of virtual links and (iv) the TT static schedules, such that all frames are schedulable and the worst-case end-to-end delay of the RC messages is minimized. We have proposed a Tabu Search-based metaheuristic for this optimization problem. The proposed algorithm has been evaluated using several benchmarks.

The optimization approaches have also been evaluated using realistic aerospace case studies. In this context, we have shown how to extend the proposed optimization frameworks to also take into account quality of service constraints. For TTEthernet networks, we have also proposed a topology selection method to reduce the cost of the architecture.

# Summary (Danish)

Et mikset-kritikalitets system implementerer applikationer med forskellige sikkerhedskritikalitets niveauer på samme platform. I sådanne tilfælde kræver certificering standarderne at applikationer fra forskellige kritikalitets niveauer er beskyttede, så de ikke kan påvirke hinanden. Ellers skal alle opgaver udvikles og certificeres i henhold til det højeste kritikalitet niveau, hvilket dramatisk øger udviklingsomkostningerne. I denne afhandling betragter vi mikset-kritikalitets realtidsapplikationer implementeret på distribuerede partitionerede arkitekturer.

Partitionerede arkitekturer benytter tidsmæssige og rumlige separations mekanismer for at sikre, at applikationer fra de forskellige kritikalitets niveauer ikke forstyrrer hinanden. I tidsmæssig opdeling får hver applikation kun lov til at køre inden for fastlagte tidsintervaller, fordelt på hver processor. Rækkefølgen af disse tidsintervaller, for alle applikationerne på en processor, er grupperet i en Major Frame, der gentages med jævne mellemrum. Hver partition kan have sin egen planlægnings politik; vi har betragtet ikke forebyggende statisk cyklisk planlægning og fast prioriterede planlægnings politikker. Vi antager, at kommunikationsnetværket implementere TTEthernet protokollen, som understøtter tidsudløste (TT) meddelelser, der sendes baseret på statiske planlægnings tabeller, rate begrænset (RC) meddelelser, med afgrænset ende-til-ende forsinkelse, og bedste forsøgs (BE) beskeder, for hvilke der ikke gives timing garantier. TTEthernet tilbyder rumlig separation af mikset-kritikalitets beskeder via virtuelle forbindelser, og tidsmæssig separation, gennemføres ved tidsplans tabeller for TT beskeder og båndbredde tildeling for RC meddelelser.

Formålet med denne afhandling er at udvikle metoder og værktøjer til distribuerede mikset-kritikalitets realtidssystemer. På processor niveau, er vi interesseret i at bestemme (i) kortlægning af opgaver til processorer, (ii) tildeling af opgaver til partitioner, (iii) nedbrydning af opgaver i redundant mindre kritiske opgaver, (iv) sekvensen og størrelse af partition tidsintervaller på hver processor og (v) tidsplans tabeller, således at alle applikationer kan planlægges og udviklings og certificerings omkostninger minimeres. Vi har foreslået Simulated Annealing and Tabu Search metaheuristikker til at løse disse

optimeringsproblemer. De foreslåede algoritmer er blevet evalueret ved hjælp af flere benchmarks.

På kommunikations og netværks niveau, er vi interesserede i design optimering af TTEthernet netværk, der anvendes til at overføre mikset-kritikalitets beskeder. Givet et sæt af TT og RC-beskeder, og topologien af netværket, er vi interesseret i at optimere (i) pakning af meddelelser i frames, (ii) tildeling af frames til virtuelle links, (iii) routing af virtuelle links og (iv) TT statiske tabeller, således at alle frames kan planlægges og den værst tænkelige ende-til-ende forsinkelse af RC-beskeder bliver minimeret. Vi har foreslået en Tabu Search-baseret metaheuristik til dette optimerings problem. Den foreslåede algoritme er blevet evalueret ved hjælp af flere benchmarks.

Optimerings metoderne er også blevet evalueret ved brug af realistiske rumfart casestudier. I denne sammenhæng har vi vist, hvordan man kan udvide det foreslåede optimerings framework til også at tage hensyn til service og kvalitets begrænsninger. For TTEthernet netværk har vi også foreslået en topologi udvælgelses metode der reducere omkostningerne i arkitekturen.

## Preface

This thesis was prepared at the Department of Applied Mathematics and Computer Science, Technical University of Denmark in fulfillment of the requirements for acquiring the Ph.D. degree in computer engineering.

The thesis deals with methods and tools for the optimization of mixed-criticality realtime embedded systems, to support the system engineers in the early life cycles phases, where the impact of design decisions is greatest.

The work has been supervised by Associate Professor Paul Pop and co-supervised by Professor Jan Madsen.

Lyngby, 31 January 2014

Domițian Tămaş-Selicean

## Papers Included in the Thesis

- Domiţian Tămaş-Selicean and Paul Pop. Optimization of Time-Partitions for Mixed-Criticality Real-Time Distributed Embedded Systems. Proceedings of the International Symposium on Object/Component/Service-Oriented Real-Time Distributed Computing Workshops, 2011. Published.

- Domiţian Tămaş-Selicean and Paul Pop. Design Optimization of Mixed-Criticality Real-Time Applications on Cost-Constrained Partitioned Architectures. *Proceedings of the Real-Time Systems Symposium*, pp. 24–33, 2011. Published.

- Domiţian Tămaş-Selicean and Paul Pop. Task Mapping and Partition Allocation for Mixed-Criticality Real-Time Systems. *Proceedings of the Pacific Rim International Symposium on Dependable Computing*, pp. 282–283, 2011. Published.

- Sorin O. Marinescu, Domiţian Tămaş–Selicean and Paul Pop. Timing Analysis of Mixed-Criticality Hard Real-Time Applications Implemented on Distributed Partitioned Architectures. *Proceedings of the International Conference* on Emerging Technologies and Factory Automation, pp. 1–4, 2012. Published.

- Domiţian Tămaş-Selicean, Paul Pop and Wilfried Steiner. Synthesis of Communication Schedules for TTEthernet-Based Mixed-Criticality Systems. *Proceedings of the International Conference on Hardware/Software Codesign and System Synthesis*, pp. 473–482, 2012. Published.

- Domiţian Tămaş-Selicean, Sorin O. Marinescu and Paul Pop. Analysis and Optimization of Mixed-Criticality Applications on Partitioned Distributed Architectures. *Proceedings of the IET System Safety Conference*, pp. 1–6, 2012. Published.

- Domiţian Tămaş-Selicean, Didier Keymeulen, Dan Berisford, Robert Carlson, Kevin Hand, Paul Pop, Winthrop Wadsworth and Ralph Levy. Fourier Transform Spectrometer Controller for Partitioned Architectures. *Proceedings of the Aerospace Conference*, pp. 1–11, 2013. Published.

- Domiţian Tămaş-Selicean and Paul Pop. Design Optimization of Mixed-Criticality Real-Time Systems. Under review in *ACM Transactions on Embedded Computing*.

- Domiţian Tămaş-Selicean, Paul Pop and Wilfried Steiner. Design Optimization of TTEthernet-based Distributed Real-Time Systems. Under review in *Real-Time Systems Journal*.

## Acknowledgements

I cannot thank Paul Pop enough for his tireless help, continuous involvement and friendship. His guidance and encouragement were a motivating force throughout my PhD. I also want to thank Jan Madsen for our insightful conversations and the opportunities he has created. My Phd studies were not only extremely interesting, but also inspiring due to their supervision, help and support.

I would also like to thank my friends and colleagues at DTU Compute, for creating a fun work environment and making the PhD life more pleasant. Special thanks goes to Karin Tunder for her constant help with the administrative tasks and impromptu Danish lessons, to Mads Ingwar for translating the summary, and to Michael Reibel Boesen for his help and door-opening networking. I appreciate the support provided by the administrative and technical staff.

I am grateful to Wilfried Steiner from TTTech Computertechnik AG, Vienna for our collaboration and his hospitality. His in-depth suggestions have been of big help in this work. Many thanks to the people at the Jet Propulsion Laboratory, NASA for the hospitality, and especially to Didier Keymeulen, for his guidance during my external stay and for making a dream come true. I am grateful to the ARTEMIS Joint Under-taking for funding my PhD project, and to Oticon Fonden and Otto Mønsteds Fond for funding my external research stay.

Last but not least, I am profoundly grateful for their love and patience to my family and friends.

<u>x</u>\_\_\_\_\_

\_

#### Contents

| Su | mma    | ry                            | i   |

|----|--------|-------------------------------|-----|

| Su | mma    | ry (Danish)                   | iii |

| Pr | eface  |                               | v   |

| Pa | pers ] | Included in the Thesis        | vii |

| Ac | know   | ledgements                    | ix  |

| Ab | brevi  | ations                        | xxi |

| No | tatio  | ns                            | XXV |

| 1  | Intro  | oduction                      | 1   |

|    | 1.1    | Mixed-Criticality Systems     | 2   |

|    | 1.2    | Partitioned Architectures     | 3   |

|    | 1.3    | Embedded Systems Design       | 6   |

|    | 1.4    | Design Space Exploration      | 10  |

|    | 1.5    | Research Contributions        | 12  |

|    | 1.6    | Thesis Overview               | 15  |

|    | 1.7    | Related Work                  | 17  |

| 2  | Syste  | em Model                      | 23  |

|    | 2.1    | Application Model             | 23  |

|    |        | 2.1.1 Safety Integrity Levels | 24  |

|    |        | 2.1.2 Task Decomposition      | 26  |

|    |        | 2.1.3 Development Cost Model  | 28  |

|    |        | 2.1.4 Protection Requirements | 29  |

|   | 2.2  | Archite  | ecture Model                                    | 30 |

|---|------|----------|-------------------------------------------------|----|

|   |      | 2.2.1    | Partitioning at PE-Level                        | 30 |

|   |      |          | 2.2.1.1 Elevation and Software-Based Protection | 31 |

|   |      | 2.2.2    | Communication Network Model                     | 33 |

|   |      |          | 2.2.2.1 Frames                                  | 34 |

|   |      | 2.2.3    | The TTEthernet Protocol                         | 36 |

|   |      |          | 2.2.3.1 Time-Triggered Transmission             | 38 |

|   |      |          | 2.2.3.2 Rate Constrained Transmission           | 39 |

| 3 | Desi | gn Opti  | imizations at the Processor-Level               | 43 |

|   | 3.1  | -        | m Formulation                                   | 44 |

|   |      | 3.1.1    | Optimization of Time-Partitions                 | 44 |

|   |      | 3.1.2    | Partition-Aware Mapping Optimization            | 47 |

|   |      | 3.1.3    | Partition-Sharing Optimization                  | 49 |

|   |      | 3.1.4    | Task Decomposition                              | 50 |

|   | 3.2  | Design   | Optimization Strategies                         | 54 |

|   |      | 3.2.1    | Optimization of Time-Partitions                 | 54 |

|   |      | 3.2.2    | Tabu Search-Based Design Optimization           | 57 |

|   | 3.3  | Degree   | e of Schedulability                             | 66 |

|   | 3.4  |          | cheduling                                       | 66 |

|   | 3.5  |          | nse Time Analysis                               | 67 |

|   | 3.6  | Experi   | mental Results                                  | 69 |

|   |      | 3.6.1    | Optimization of Time-Partition                  | 69 |

|   |      | 3.6.2    | Mixed-Criticality Design Optimization           | 72 |

| 4 | Desi | ign Opti | imizations at the Network-Level                 | 77 |

|   | 4.1  |          | m Formulation                                   | 77 |

|   |      | 4.1.1    | Straightforward Solution                        | 78 |

|   |      | 4.1.2    | Message Fragmenting and Packing                 | 82 |

|   |      | 4.1.3    | Virtual Link Routing                            | 84 |

|   |      | 4.1.4    | Scheduling of TT Messages                       | 84 |

|   | 4.2  | Design   | Optimization Strategy                           | 86 |

|   |      | 4.2.1    | Tabu Search                                     | 88 |

|   |      | 4.2.2    | Design Transformations                          | 90 |

|   |      | 4.2.3    | Candidate List                                  | 93 |

|   |      |          | 4.2.3.1 Candidates for TT Frames                | 93 |

|   |      |          | 4.2.3.2 Candidates for RC Frames                | 94 |

|   |      |          | 4.2.3.3 Randomly Generated Candidates           | 95 |

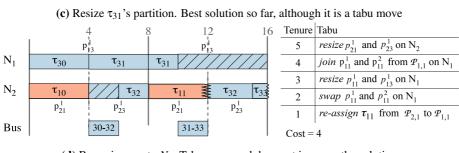

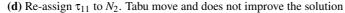

|   |      | 4.2.4    | Tabu Search Example                             | 95 |

|   | 4.3  | Experi   | mental Evaluation                               | 98 |

| 5  | Desi   | gn Opti  | imizations | for Mixed-Criticality Space Applications             | 103   |

|----|--------|----------|------------|------------------------------------------------------|-------|

|    | 5.1    | Backgi   | round      |                                                      | 104   |

|    | 5.2    | Proces   | sor-Level  | Partitioning                                         | 105   |

|    |        | 5.2.1    | Mars Pat   | hfinder Mission                                      | 105   |

|    |        | 5.2.2    | Fourier 7  | ransform Spectrometer Controller for Partitioned Ar- |       |

|    |        |          | chitectur  | es                                                   | 107   |

|    |        |          | 5.2.2.1    | Fourier Transform Spectrometry                       | 108   |

|    |        |          | 5.2.2.2    | Compositional InfraRed Imaging Spectrometer (CIRIS   | S)110 |

|    |        |          | 5.2.2.3    | CIRIS Controller Implementation                      | 111   |

|    |        |          | 5.2.2.4    | Evaluation of CIRIS                                  | 119   |

|    |        |          | 5.2.2.5    | Controller Application Model for Integration with    |       |

|    |        |          |            | MESUR                                                | 123   |

|    |        |          | 5.2.2.6    | Quality of Service (QoS)                             | 125   |

|    |        |          | 5.2.2.7    | Influence of Partitioning on QoS                     | 125   |

|    |        |          | 5.2.2.8    | Running Signal-to-Noise Ratio (SNR)                  | 127   |

|    | 5.3    | Comm     | unication- | Level Partitioning                                   | 127   |

|    | 5.4    | Evalua   | tion       |                                                      | 129   |

|    |        | 5.4.1    | Processo   | r-Level Partitioning                                 | 129   |

|    |        | 5.4.2    | Commun     | ication-Level Partitioning                           | 134   |

|    |        |          | 5.4.2.1    | Topology Selection                                   | 134   |

|    |        |          | 5.4.2.2    | Optimization for Best-Effort Traffic                 | 137   |

| 6  | Con    | clusions | s and      |                                                      |       |

|    | Futu   | ire Wor  | k          |                                                      | 139   |

|    | 6.1    | Conclu   | isions     |                                                      | 139   |

|    | 6.2    | Future   | Work       |                                                      | 142   |

| Bi | bliogı | aphy     |            |                                                      | 145   |

## List of Figures

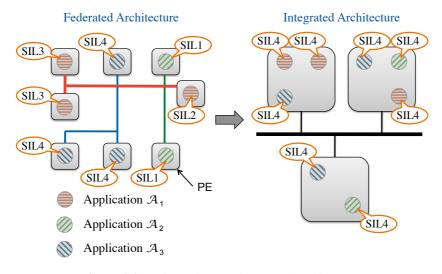

| 1.1   | Federated versus integrated architectures                        | 4  |

|-------|------------------------------------------------------------------|----|

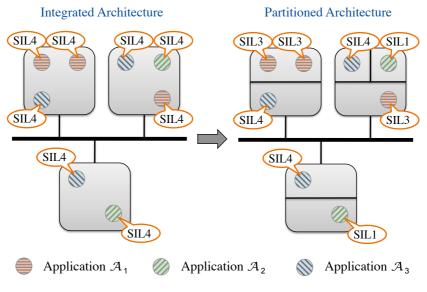

| 1.2   | Integrated versus partitioned architectures                      | 5  |

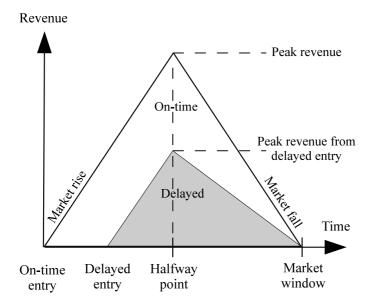

| 1.3   | Revenue impact of delayed entry                                  | 8  |

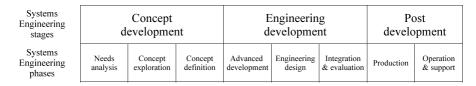

| 1.4   | A systems engineering life cycle model (from [105])              | 9  |

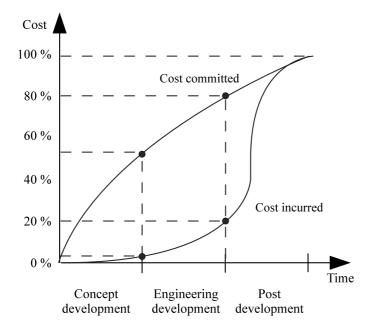

| 1.5   | Cost committed versus cost incurred during the system life cycle | 10 |

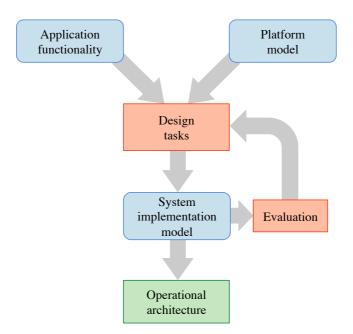

| 1.6   | Design Space Exploration                                         | 11 |

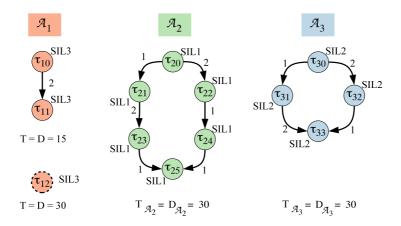

| 2.1   | Application model example                                        | 25 |

| 2.2   | Partitioned architecture                                         | 31 |

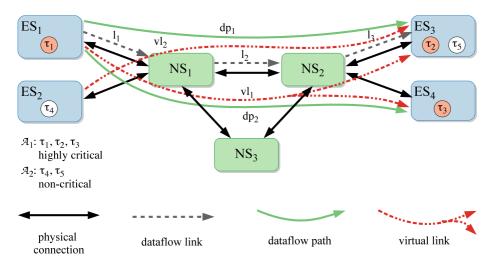

| 2.3   | TTEthernet cluster example                                       | 34 |

| 2.4   | Simplified frame format                                          | 35 |

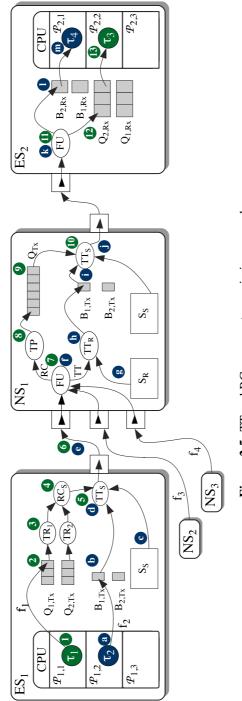

| 2.5   | TT and RC message transmission example                           | 37 |

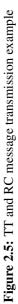

| 2.6   | Multiplexing two RC frames                                       | 40 |

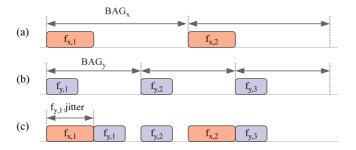

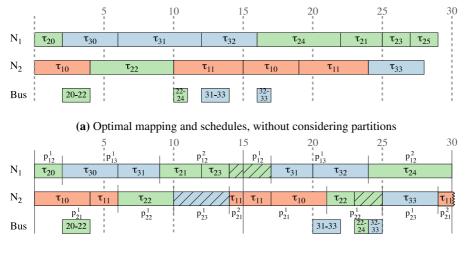

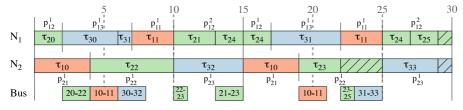

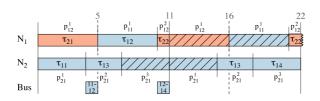

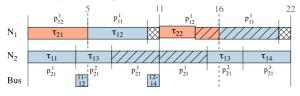

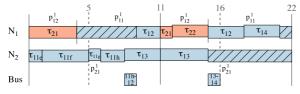

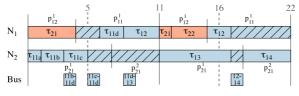

| 3.1   | Motivational example                                             | 45 |

| 3.2   | Motivational example                                             | 48 |

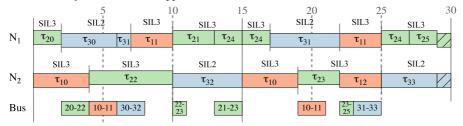

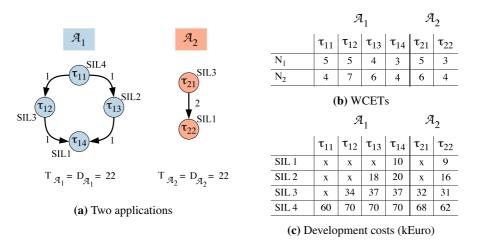

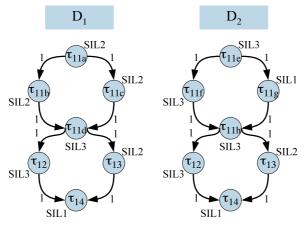

| 3.3   | Application model example for SIL decomposition                  | 51 |

| 3.4   | Example decomposition for task $\tau_{11}$                       | 52 |

| 3.5   | SIL decomposition optimization example                           | 53 |

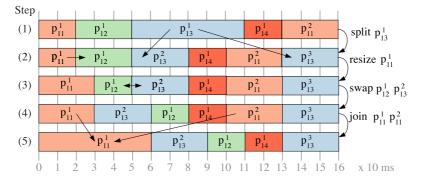

| 3.6   | Time-Partition Optimization                                      | 55 |

| 3.7   | The Simulated Annealing algorithm                                | 56 |

| 3.8   | Partition slice move examples                                    | 57 |

| 3.9   | Mixed-Criticality Design Optimization strategy                   | 58 |

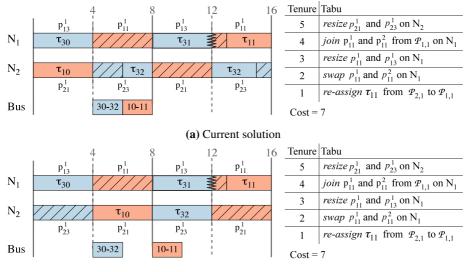

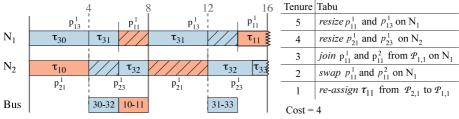

| 3.10  | The Tabu Search algorithm                                        | 59 |

| 3.11  | Moves and tabu history                                           | 62 |

|       | Algorithm to generate the candidate list $C$                     | 65 |

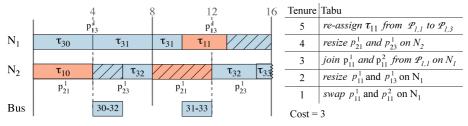

| 3 1 3 | Availability and demand                                          | 68 |

| 4.1  | Example system model                                                        | 79   |

|------|-----------------------------------------------------------------------------|------|

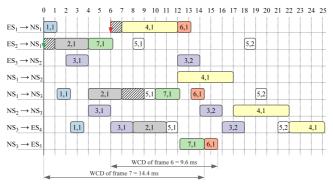

| 4.2  | Baseline solutions                                                          | 80   |

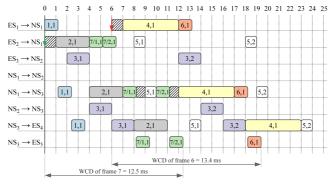

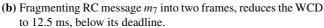

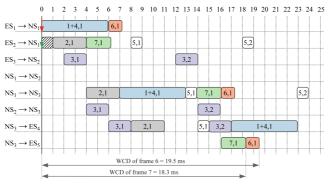

| 4.3  | Message packing and fragmenting example                                     | 83   |

| 4.4  | Message rerouting examples                                                  | 85   |

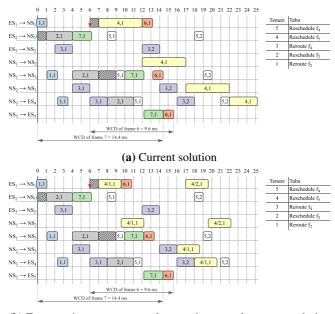

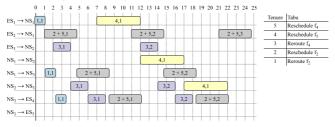

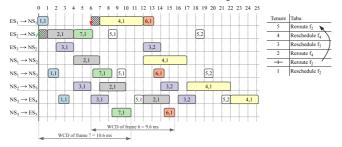

| 4.5  | Rescheduling frame $f_5$ to an earlier instant on $[ES_2, NS_1]$ groups the |      |

|      | TT frames and eliminates the timely block intervals, resulting in the       |      |

|      | WCD of the RC messages                                                      | 86   |

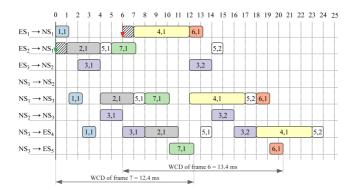

| 4.6  | Design Optimization of TTEthernet-based Systems                             | 87   |

| 4.7  | The Tabu Search algorithm                                                   | 89   |

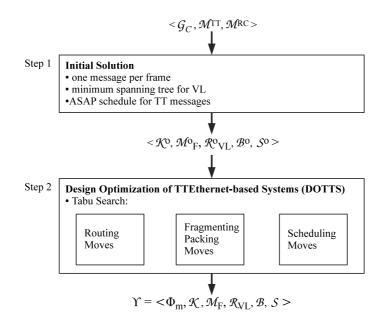

| 4.8  | Representation of a frame as a tree                                         | 92   |

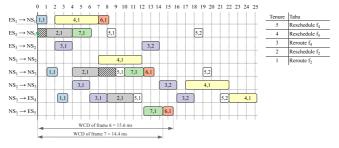

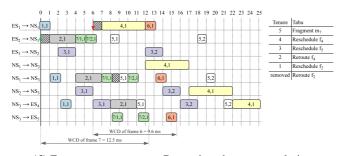

| 4.9  | Candidate solutions and their tabu list                                     | 96   |

| 4.9  | Candidate solutions and their tabu list                                     | 97   |

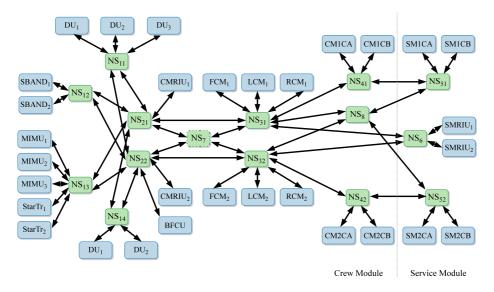

| 4.10 | Network topology of the Orion CEV, derived from [126]                       | 100  |

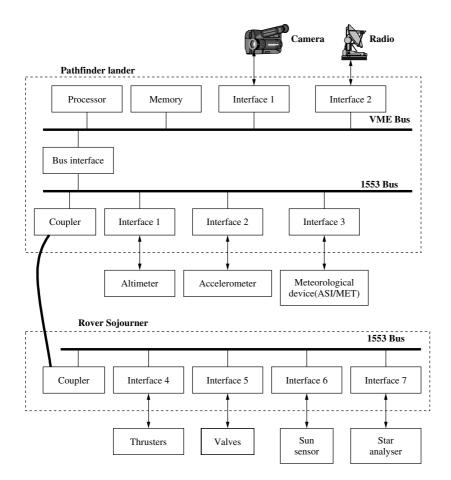

| 5.1  | Hardware architecture of the Pathfinder spacecraft (from [63])              | 106  |

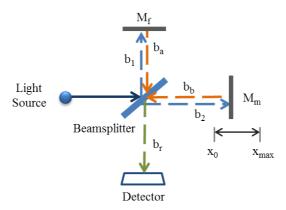

| 5.2  | Basic Michelson interferometer                                              | 109  |

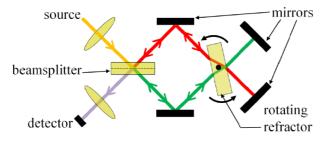

| 5.3  | CIRIS interferometer (from [45])                                            | 110  |

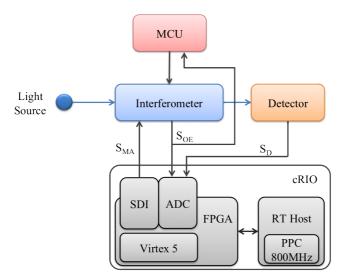

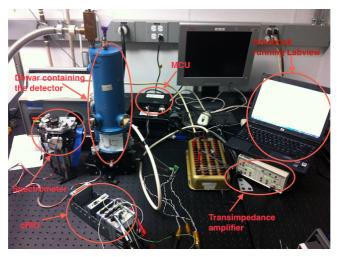

| 5.4  | CIRIS setup                                                                 | 112  |

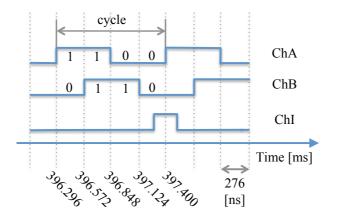

| 5.5  | Optical encoder output channels logic states                                | 113  |

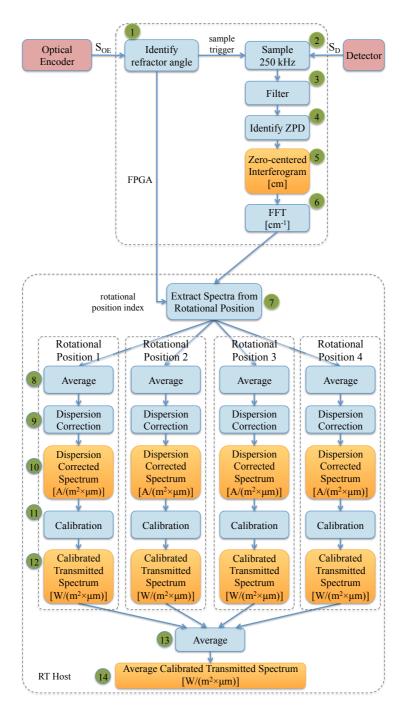

| 5.6  | CIRIS high-level acquisition and processing algorithm description           | 115  |

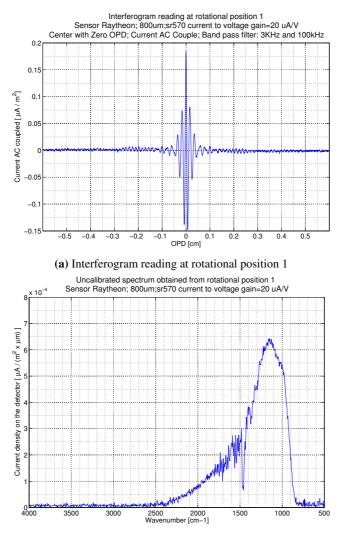

| 5.7  | Interferogram and resulting spectrum                                        | 116  |

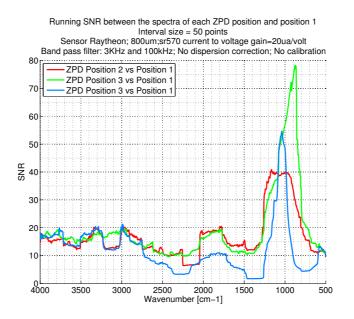

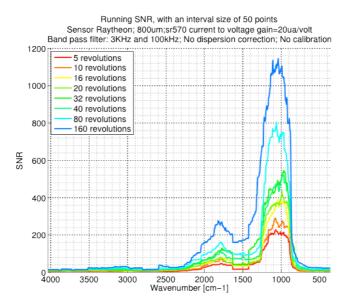

| 5.8  | Running SNR comparison between the spectra at different ZPD position        | s117 |

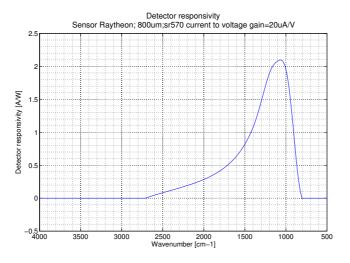

| 5.9  | Detector responsivity                                                       | 118  |

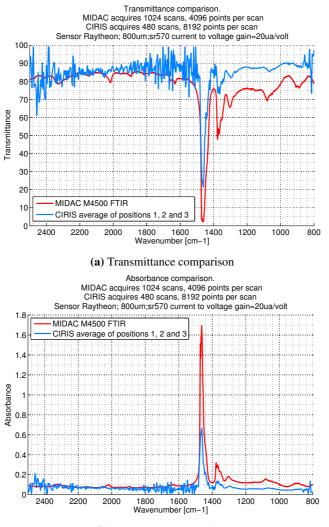

| 5.10 | Comparison between the results obtained with CIRIS and with MIDAC           |      |

|      | M4500 FITR                                                                  | 120  |

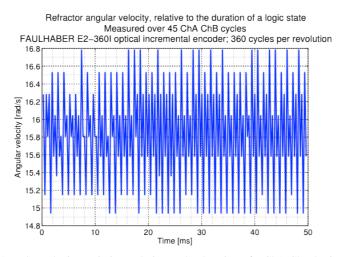

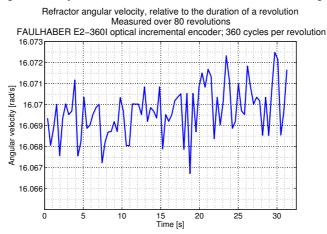

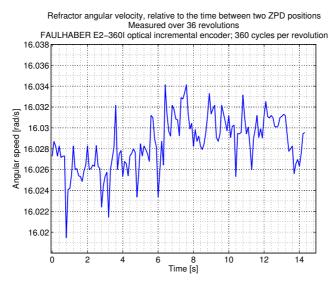

| 5.11 | Angular velocity variation                                                  | 121  |

| 5.11 | Angular velocity variation                                                  | 122  |

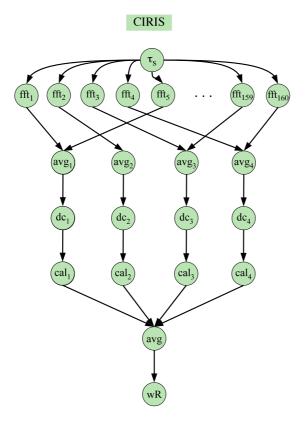

| 5.12 | CIRIS task graph                                                            | 124  |

|      | Comparison of running SNR of an interval size of 50 points, over dif-       |      |

|      | ferent number of revolutions                                                | 126  |

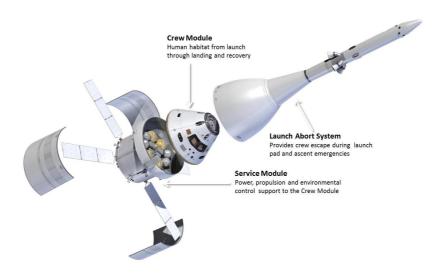

| 5.14 | Orion major elements (from [121])                                           | 128  |

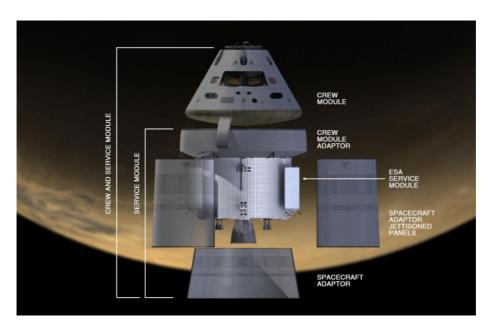

|      | Location of ESM on Orion (from [121])                                       | 128  |

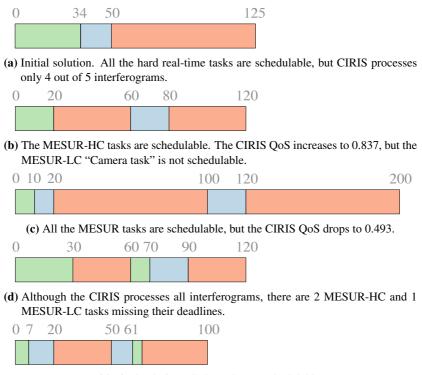

|      | Partition table configurations                                              | 131  |

|      | Topology Selection with DOTTS                                               | 135  |

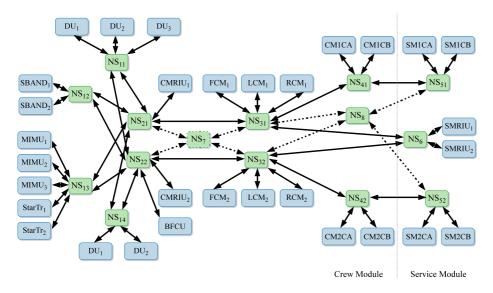

|      | Network topology of the Orion CEV, derived from [126]                       | 136  |

|      |                                                                             |      |

xvii

### List of Tables

| 2.1        | ISO/DIS 26262 SIL decomposition schemes                  | 27       |

|------------|----------------------------------------------------------|----------|

| 3.1<br>3.2 | TPO experimental results                                 | 71<br>74 |

| 4.1        | DOTTS experimental results                               | 99       |

| 5.1        | Pathfinder mission, exploration mode task set parameters | 107      |

| 5.2        | Rotating refractor velocity mean and standard deviation  | 122      |

| 5.3        | Logic state numbers of the ZPD positions                 | 123      |

| 5.4        | CIRIS task details                                       | 125      |

| 5.5        | Partition table configuration                            | 132      |

| 5.6        | Topology selection experimental results                  | 136      |

| 5.7        | Optimization of BE traffic experimental results          | 138      |

|            |                                                          |          |

# Abbreviations

| Abbreviation | Meaning                                         |

|--------------|-------------------------------------------------|

| ABS          | Anti-lock Braking System                        |

| ADC          | Analog-Digital Converter                        |

| AGC          | Apollo Guidance Computer                        |

| ASAP         | As-Soon-As-Possible (ASAP)                      |

| ASIL         | Automotive Safety Integrity Level               |

| AVB          | Audio Video Bridging                            |

| BAG          | Bandwidth Allocation Gap                        |

| BE           | Best-Effort                                     |

| BEO          | Beyond Earth Orbit                              |

| CA           | Certification Authority                         |

| CAN          | Controller Area Network                         |

| CBS          | Constant Bandwidth Server                       |

| CEV          | Crew Exploration Vehicle                        |

| ChA ChB      | Channel A, Channel B                            |

| ChI          | Channel I                                       |

| CIRIS        | Compositional InfraRed Imaging Spectrometer     |

| CLG          | Candidate List Generation                       |

| COCOMO       | Constructive Cost Model                         |

| СМ           | Crew Module                                     |

| CPU          | Central Processing Unit                         |

| cRIO         | CompactRIO                                      |

| DAC          | Digital-Analog Converter                        |

| DAL          | Design Assurance Level                          |

| DC           | Development Cost                                |

| DOTTS        | Design Optimization of TTEthernet-based Systems |

| DSE   | Design Space Exploration                                       |

|-------|----------------------------------------------------------------|

| ECU   | Electronic Control Unit                                        |

| EDF   | Earliest Deadline First                                        |

| ES    | End System                                                     |

| ESA   | European Space Agency                                          |

| ESes  | End Systems                                                    |

| ESM   | European Service Module                                        |

| ET    | Event-Triggered                                                |

| FFT   | Fast Fourier Transform                                         |

| FIFO  | First In First Out                                             |

| FPGA  | Field-Programmable Gate Array                                  |

| FPS   | Fixed-Priority Scheduling                                      |

| FTIR  | Fourier Transform Infrared Spectrometer                        |

| FTS   | Fourier Transform Spectrometer                                 |

| FU    | Filtering Unit                                                 |

| IAP   | Interferogram Acquisition Process                              |

| IC    | Integrated Circuit                                             |

| ILP   | Integer Linear Programming                                     |

| IMA   | Integrated Modular Avionics                                    |

| ISS   | International Space Station                                    |

| JPL   | Jet Propulsion Laboratory                                      |

| LAS   | Launch Abort System                                            |

| LCM   | Least-Common Multiplier                                        |

| LS    | List Scheduling                                                |

| MCDO  | Mixed-Criticality Design Optimization                          |

| MCU   | Motor Control Unit                                             |

| MESUR | Mars Environment Survey Pathfinder                             |

| MF    | Major Frame                                                    |

| MMU   | Memory Management Unit                                         |

| MO    | Mapping Optimization                                           |

| MO+PO | Optimization approach where MO is performed separately from PO |

| MPCV  | Multi-Purpose Crew Vehicle                                     |

| MPO   | Simultaneous Mapping and Partitioning Optimization             |

| NASA  | National Aeronautics and Space Administration                  |

| NC    | Non-Critical                                                   |

| NIC   | Network Interface Card                                         |

| NRE   | Non-Recursive Engineering                                      |

| NS    | Network Switch                                                 |

| NSes  | Network Switches                                               |

| OPD   | Optical Path Difference                                        |

| PA    | Partitioned Architecture                                       |

| PCPersonal ComputerPCIPPriority-and-Criticality Inversion ProtocolPCCPPriority-and-Criticality Ceiling ProtocolPEProcessing ElementPFOPacking and Fragmenting OptimizationQoSQuality-of-ServiceRCRate-ConstrainedRMRate MonotonicRORouting OptimizationROMRead-only MemoryRTOSReal-Time Operating SystemSASimulated AnnealingSCSafety-CriticalSCASpacecraft AdapterSCSStatic Cyclic SchedulingSDIStepper Drive InterfaceSFISoftware Fault IsolationSILSafety-Integrity LevelSMService ModuleSMTSatisfiability Modulo TheorySNRSignal-to-Noise RatioSOScheduling OptimizationSWAPSize, Weight and PowerSysMLSystems Modeling Language |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCCPPriority-and-Criticality Ceiling ProtocolPEProcessing ElementPFOPacking and Fragmenting OptimizationPOPartitioning OptimizationQoSQuality-of-ServiceRCRate-ConstrainedRMRate MonotonicRORouting OptimizationROMRead-only MemoryRTOSReal-Time Operating SystemSASimulated AnnealingSCSafety-CriticalSCASpacecraft AdapterSCSStatic Cyclic SchedulingSDIStepper Drive InterfaceSFISoftware Fault IsolationSILSafety-Integrity LevelSMService ModuleSMTSatisfiability Modulo TheorySNRSignal-to-Noise RatioSOScheduling OptimizationSSStraightforward SolutionSWaPSize, Weight and Power                                            |

| PEProcessing ElementPFOPacking and Fragmenting OptimizationPOPartitioning OptimizationQoSQuality-of-ServiceRCRate-ConstrainedRMRate MonotonicRORouting OptimizationROMRead-only MemoryRTOSReal-Time Operating SystemSASimulated AnnealingSCSafety-CriticalSCASpacecraft AdapterSCSStatic Cyclic SchedulingSDIStepper Drive InterfaceSFISoftware Fault IsolationSILSafety-Integrity LevelSMService ModuleSMTSatisfiability Modulo TheorySNRSignal-to-Noise RatioSOScheduling OptimizationSSStraightforward SolutionSWaPSize, Weight and Power                                                                                         |

| PFOPacking and Fragmenting OptimizationPOPartitioning OptimizationQoSQuality-of-ServiceRCRate-ConstrainedRMRate MonotonicRORouting OptimizationROMRead-only MemoryRTOSReal-Time Operating SystemSASimulated AnnealingSCSafety-CriticalSCASpacecraft AdapterSCSStatic Cyclic SchedulingSDIStepper Drive InterfaceSFISoftware Fault IsolationSILSafety-Integrity LevelSMService ModuleSMRSignal-to-Noise RatioSOScheduling OptimizationSSStraightforward SolutionSWaPSize, Weight and Power                                                                                                                                            |

| POPartitioning OptimizationQoSQuality-of-ServiceRCRate-ConstrainedRMRate MonotonicRORouting OptimizationROMRead-only MemoryRTOSReal-Time Operating SystemSASimulated AnnealingSCSafety-CriticalSCASpacecraft AdapterSCSStatic Cyclic SchedulingSDIStepper Drive InterfaceSFISoftware Fault IsolationSILSafety-Integrity LevelSMService ModuleSMRSignal-to-Noise RatioSOScheduling OptimizationSSStraightforward SolutionSWaPSize, Weight and Power                                                                                                                                                                                   |

| RCRate-ConstrainedRMRate-ConstrainedRMRate MonotonicRORouting OptimizationROMRead-only MemoryRTOSReal-Time Operating SystemSASimulated AnnealingSCSafety-CriticalSCASpacecraft AdapterSCSStatic Cyclic SchedulingSDIStepper Drive InterfaceSFISoftware Fault IsolationSILSafety-Integrity LevelSMService ModuleSNRSignal-to-Noise RatioSOScheduling OptimizationSSStraightforward SolutionSWaPSize, Weight and Power                                                                                                                                                                                                                 |

| RMRate MonotonicRORouting OptimizationROMRead-only MemoryRTOSReal-Time Operating SystemSASimulated AnnealingSCSafety-CriticalSCASpacecraft AdapterSCSStatic Cyclic SchedulingSDIStepper Drive InterfaceSFISoftware Fault IsolationSILSafety-Integrity LevelSMService ModuleSMTSatisfiability Modulo TheorySNRSignal-to-Noise RatioSOScheduling OptimizationSSStraightforward SolutionSWaPSize, Weight and Power                                                                                                                                                                                                                      |

| RORouting OptimizationROMRead-only MemoryRTOSReal-Time Operating SystemSASimulated AnnealingSCSafety-CriticalSCASpacecraft AdapterSCSStatic Cyclic SchedulingSDIStepper Drive InterfaceSFISoftware Fault IsolationSILSafety-Integrity LevelSMService ModuleSMTSatisfiability Modulo TheorySNRSignal-to-Noise RatioSOScheduling OptimizationSSStraightforward SolutionSWaPSize, Weight and Power                                                                                                                                                                                                                                      |

| ROMRead-only MemoryRTOSReal-Time Operating SystemSASimulated AnnealingSCSafety-CriticalSCASpacecraft AdapterSCSStatic Cyclic SchedulingSDIStepper Drive InterfaceSFISoftware Fault IsolationSILSafety-Integrity LevelSMService ModuleSMTSatisfiability Modulo TheorySNRSignal-to-Noise RatioSOScheduling OptimizationSSStraightforward SolutionSWaPSize, Weight and Power                                                                                                                                                                                                                                                            |

| RTOSReal-Time Operating SystemSASimulated AnnealingSCSafety-CriticalSCASpacecraft AdapterSCSStatic Cyclic SchedulingSDIStepper Drive InterfaceSFISoftware Fault IsolationSILSafety-Integrity LevelSMService ModuleSMTSatisfiability Modulo TheorySNRSignal-to-Noise RatioSOScheduling OptimizationSSStraightforward SolutionSWaPSize, Weight and Power                                                                                                                                                                                                                                                                               |

| SASimulated AnnealingSCSafety-CriticalSCASpacecraft AdapterSCSStatic Cyclic SchedulingSDIStepper Drive InterfaceSFISoftware Fault IsolationSILSafety-Integrity LevelSMService ModuleSMTSatisfiability Modulo TheorySNRSignal-to-Noise RatioSOScheduling OptimizationSSStraightforward SolutionSWaPSize, Weight and Power                                                                                                                                                                                                                                                                                                             |

| SCSafety-CriticalSCASpacecraft AdapterSCSStatic Cyclic SchedulingSDIStepper Drive InterfaceSFISoftware Fault IsolationSILSafety-Integrity LevelSMService ModuleSMTSatisfiability Modulo TheorySNRSignal-to-Noise RatioSOScheduling OptimizationSSStraightforward SolutionSWaPSize, Weight and Power                                                                                                                                                                                                                                                                                                                                  |

| SCSafety-CriticalSCASpacecraft AdapterSCSStatic Cyclic SchedulingSDIStepper Drive InterfaceSFISoftware Fault IsolationSILSafety-Integrity LevelSMService ModuleSMTSatisfiability Modulo TheorySNRSignal-to-Noise RatioSOScheduling OptimizationSSStraightforward SolutionSWaPSize, Weight and Power                                                                                                                                                                                                                                                                                                                                  |

| SCS       Static Cyclic Scheduling         SDI       Stepper Drive Interface         SFI       Software Fault Isolation         SIL       Safety-Integrity Level         SM       Service Module         SMT       Satisfiability Modulo Theory         SNR       Signal-to-Noise Ratio         SO       Scheduling Optimization         SS       Straightforward Solution         SWaP       Size, Weight and Power                                                                                                                                                                                                                 |

| SDIStepper Drive InterfaceSFISoftware Fault IsolationSILSafety-Integrity LevelSMService ModuleSMTSatisfiability Modulo TheorySNRSignal-to-Noise RatioSOScheduling OptimizationSSStraightforward SolutionSWaPSize, Weight and Power                                                                                                                                                                                                                                                                                                                                                                                                   |

| SFI       Software Fault Isolation         SIL       Safety-Integrity Level         SM       Service Module         SMT       Satisfiability Modulo Theory         SNR       Signal-to-Noise Ratio         SO       Scheduling Optimization         SS       Straightforward Solution         SWaP       Size, Weight and Power                                                                                                                                                                                                                                                                                                      |

| SILSafety-Integrity LevelSMService ModuleSMTSatisfiability Modulo TheorySNRSignal-to-Noise RatioSOScheduling OptimizationSSStraightforward SolutionSWaPSize, Weight and Power                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SMService ModuleSMTSatisfiability Modulo TheorySNRSignal-to-Noise RatioSOScheduling OptimizationSSStraightforward SolutionSWaPSize, Weight and Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SMService ModuleSMTSatisfiability Modulo TheorySNRSignal-to-Noise RatioSOScheduling OptimizationSSStraightforward SolutionSWaPSize, Weight and Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SNR     Signal-to-Noise Ratio       SO     Scheduling Optimization       SS     Straightforward Solution       SWaP     Size, Weight and Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SO     Scheduling Optimization       SS     Straightforward Solution       SWaP     Size, Weight and Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SS         Straightforward Solution           SWaP         Size, Weight and Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SWaP Size, Weight and Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| , 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SysML Systems Modeling Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TDMA Time-Division Multiple Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TI Initial Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TL Temperature Length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TP Traffic Policing task                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TPO Time-Partitions Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TR Traffic Regulator task                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TS Tabu Search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TT Time-Triggered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TTP Time-Triggered Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VL Virtual Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| WCET Worst-Case Execution Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| WCD Worst-Case end-to-end Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ZPD Zero Optical Path Difference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

xxiv

## Notations

| Notation                                                                                                               | Meaning                                                                     |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Γ                                                                                                                      | Set of all applications in the system                                       |

| $\mathcal{A}_i \in \Gamma$                                                                                             | An application                                                              |

| $\mathcal{G}_i(\mathcal{V}_i,\mathcal{E}_i)$                                                                           | Application graph for application $\mathcal{A}_i$                           |

| $\mathcal{V}_i$                                                                                                        | Set of all the nodes in the application graph                               |

| $\mathcal{E}_i$                                                                                                        | Set of all the edges in the application graph                               |

| $\mathcal{V}$                                                                                                          | Set of all the tasks in the system                                          |

| $\mathcal{E}$                                                                                                          | Set of edges in the protection requirements graph                           |

| $	au_j \in \mathcal{V}_i$                                                                                              | One task of the application graph                                           |

| $egin{aligned} & \overline{	au_j \in \mathcal{V}_i} \ & M : \mathcal{V}_i 	o \mathcal{N} \ & M^{\circ} \end{aligned}$  | The mapping of tasks to processing elements                                 |

|                                                                                                                        | Initial mapping of tasks to processing elements                             |

| Ĺ                                                                                                                      | The library of SIL decompositions                                           |

| $D(\mathfrak{r}_i):\mathcal{V}	o\mathcal{D}_i$                                                                         | SIL decomposition function                                                  |

| $D^{\circ}$                                                                                                            | Initial decomposition of tasks, tasks are not de-                           |

|                                                                                                                        | composed                                                                    |

| $\mathcal{D}_i$                                                                                                        | Set of SIL decomposition options                                            |

| $\mathcal{N}$                                                                                                          | Set of all the PEs in the architecture                                      |

| Ni                                                                                                                     | A processing element                                                        |

| $egin{array}{c c} \mathcal{D}_i & & \ \mathcal{N}_i & & \ \hline & N_i & & \ e_{jk} \in \mathcal{E}_i & & \end{array}$ | Edge in the application graph, indicates that the                           |

|                                                                                                                        | output of $\tau_j$ is the input of $\tau_k$                                 |

| $m_i$                                                                                                                  | Message in the application graph                                            |

| $D_{\mathcal{G}_i}$                                                                                                    | Deadline of application graph $G_i$                                         |

| $\frac{D_{\mathcal{G}_i}}{T_{\mathcal{G}_i}}$                                                                          | Period of application graph $G_i$                                           |

|                                                                                                                        | WCET for $\tau_i$ on each PE $N_j$ where $\tau_i$ is considered for mapping |

| $R_i$                            | Response time of application $\mathcal{A}_i$                  |

|----------------------------------|---------------------------------------------------------------|

| $D_i$                            | Deadline of application $\mathcal{A}_i$ or of task $\tau_i$   |

| $T_i$                            | Period of task $\tau_i$                                       |

| Cost <sub>TPO</sub>              | Cost function used by TPO                                     |

| Cost <sub>MCDO</sub>             | Cost function used by MCDO                                    |

| δ                                | Degree of schedulability                                      |

| δ <sub>sched</sub>               | Percentage improvement in the degree of schedu-               |

| -scheu                           | lability                                                      |

| $\delta_{SC}$                    | Degree of schedulability for SC applications                  |

| $\delta_{NC}$                    | Degree of schedulability for NC tasks                         |

| wsc                              | Weight for SC application, used by $Cost_{TPO}$               |

| W <sub>NC</sub>                  | Weight for NC tasks, used by $Cost_{TPO}$                     |

| $\Gamma_{QoS}$                   | Subset of the soft real-time applications                     |

| $QoS(\mathcal{A}_i)$             | The quality of service for the soft real-time appli-          |

| $\sim$ ( $^{\prime\prime}$       | cation $\mathcal{A}_i$                                        |

| $SIL(\tau_i)$                    | The SIL of task $\tau_i$                                      |

| $DC(\tau_i, SIL j)$              | The development cost of $\tau_i$ and SIL j                    |

| $DC(\mathcal{A}_i)$              | The development cost of the application $A_i$                 |

| $DC(\Gamma)$                     | The development cost for the set of all the appli-            |

|                                  | cations                                                       |

| $\delta_{DC}$                    | Increase in the development costs                             |

| $\Pi(\mathcal{V},\mathcal{E})$   | Protection requirements graph                                 |

| $sr_{ij} \in \mathcal{E}$        | An edge in $\Pi$ between $\tau_i$ and $\tau_j$ means that the |

|                                  | two tasks are not allowed to share a partition                |

| $\phi:\mathcal{V}\to\mathcal{P}$ | Assignment of tasks to partitions                             |

| φ°                               | Initial assignment of tasks to partitions                     |

| $\mathscr{P}$                    | Set of partitions                                             |

| $\mathscr{P}^{\circ}$            | Initial set of partitions                                     |

| $P_j$                            | Partition                                                     |

| $\mathscr{P}_{ij}$               | Set of partition slices of $P_j$ on $N_i$                     |

| $p_{ij}^{\vec{k}}$               | The $k^{th}$ partition slice of partition $P_j$ on $N_i$      |

| T <sub>cycle</sub>               | System cycle                                                  |

| T <sub>MF</sub>                  | Period of the major                                           |

| t <sub>O</sub>                   | Partition switch overhead                                     |

| S                                | Schedule tables                                               |

| Ψ                                | Implementation                                                |

| L                                | Tabu list, or tabu history                                    |

| l                                | Tabu tenure                                                   |

| С                                | Candidate list                                                |

| Lready                           | Sorted priority list used by List Scheduling                  |

| 3                                | Cooling ratio, used by SA                                     |

| $\mathcal{V}_C = \mathcal{ES} \cup \mathcal{N}_S$ Set of all the end systems and network switches in<br>the cluster $\mathcal{ES}$ Set of all the end systems in the cluster $\mathcal{ES}_i^{src}$ The source end system for frame $f_i$ $\mathcal{KS}$ Set of all the network switches in the cluster $\mathcal{N}_S$ Set of all the network switches in the cluster $\mathcal{N}_S$ Set of network switches that are fixed in the<br>cluster and can not be removed $\mathcal{RS}_i$ An end system $\mathcal{NS}_i$ A network switch $\mathcal{E}$ Set of physical links $\mathcal{DL}$ Set of dataflow links in the cluster $\mathcal{DL}^*$ Subset of dataflow links that are fixed in the cluster $\mathcal{DL}$ Set of dataflow links $\mathcal{DP}$ Set of dataflow link $\mathcal{DP}$ Set of dataflow paths in the cluster $dl_i$ A dataflow path $\mathcal{VL}$ Set of virtual links in the cluster $\mathcal{P}_i$ A toritual link $\mathcal{B}$ The set of BAG for all VLs $\mathcal{B}^\circ$ The initial set of BAG for all VLs $\mathcal{R}^\circ$ The initial routing of virtual links $\mathcal{M} = \mathcal{M}^{TT} \cup \mathcal{M}^{RC} \cup \mathcal{M}^{BE}$ Set of all the messages in the cluster $\mathcal{M}^{RC}$ Set of the RC messages in the cluster                                                                                                                                                                                     | $G_{\alpha}(\mathcal{Y}_{\alpha},\mathcal{F}_{\alpha})$                        | TTEthernet cluster                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------|

| the cluster $\mathcal{ES}$ Set of all the end systems in the cluster $\mathcal{ES}_i^{src}$ The source end system for frame $f_i$ $\mathcal{ES}_i^{dest}$ The set of destination end systems for frame $f_i$ $\mathcal{NS}$ Set of all the network switches in the cluster $\mathcal{NS}^*$ Subset of network switches that are fixed in the<br>cluster and can not be removed $\mathcal{ES}_i$ An end system $NS_i$ A network switch $\mathcal{E}$ Set of physical links $\mathcal{DL}$ Set of dataflow links in the cluster $\mathcal{DL}^*$ Subset of dataflow links that are fixed in the clust<br>ter and can not be removed $dl_i$ A dataflow link $\mathcal{DP}$ Set of dataflow links in the cluster $\mathcal{DL}$ Set of dataflow links in the cluster $\mathcal{DL}$ Set of dataflow link $\mathcal{DP}$ Set of dataflow paths in the cluster $dl_i$ A dataflow path $\mathcal{VL}$ Set of virtual links in the cluster $dp_i$ A dataflow path $\mathcal{VL}$ Set of virtual links in the cluster $v_{l_i}$ A virtual link $\mathcal{B}$ The set of BAG for all VLs $\mathcal{B}^\circ$ The initial set of BAG for all VLs $\mathcal{R}^\circ$ The initial routing of virtual links $\mathcal{M} = \mathcal{M}^{TT} \cup \mathcal{M}^{RC} \cup \mathcal{M}^{BE}$ Set of all the messages in the cluster $\mathcal{M}^{RC}$ Set of the RC messages in the cluster                                                                                                                                                                                                                                                          | $\frac{g_{C}(v_{C}, \mathcal{L}_{C})}{g_{L}^{2} - \mathcal{T}_{C} + g_{C}(c)}$ |                                                  |

| $\mathcal{ES}$ Set of all the end systems in the cluster $ES_i^{src}$ The source end system for frame $f_i$ $\mathcal{KS}_i^{dest}$ The set of destination end systems for frame $f_i$ $\mathcal{NS}$ Set of all the network switches in the cluster $\mathcal{NS}^{\star}$ Subset of network switches that are fixed in the<br>cluster and can not be removed $ES_i$ An end system $NS_i$ A network switch $\mathcal{E}$ Set of physical links $\mathcal{DL}$ Set of dataflow links in the cluster $\mathcal{DL}^{\star}$ Subset of dataflow links that are fixed in the clus $\mathcal{DL}$ Set of dataflow links in the cluster $\mathcal{DL}^{\star}$ Subset of dataflow links that are fixed in the clus $\mathcal{DP}$ Set of dataflow links in the cluster $\mathcal{DP}$ Set of dataflow paths in the cluster $\mathcal{DP}$ Set of furtual links in the cluster $\mathcal{PL}$ Set of virtual links in the cluster $\mathcal{PL}$ Set of provide of $\mathcal{PL}$ $\mathcal{PL}$ Set of virtual links in the cluster $\mathcal{PL}$ Set of virtual links $\mathcal{PL}$ Set of BAG for all VLs $\mathcal{R}^{\circ}$ The initial routing of virtual links $\mathcal{M} = \mathcal{M}^{TT} \cup \mathcal{M}^{RC} \cup \mathcal{M}^{BE}$ Set of all the messages | $V_C = LS \cup MS$                                                             | -                                                |

| $ES_i^{src}$ The source end system for frame $f_i$ $\mathcal{LS}_i^{dest}$ The set of destination end systems for frame $f_i$ $\mathcal{NS}$ Set of all the network switches in the cluster $\mathcal{NS}^{\star}$ Subset of network switches that are fixed in the<br>cluster and can not be removed $ES_i$ An end system $NS_i$ A network switch $\mathcal{E}$ Set of physical links $\mathcal{DL}$ Set of dataflow links in the cluster $\mathcal{DL}^{\star}$ Subset of dataflow links that are fixed in the clus $\mathcal{DL}$ Set of dataflow links in the cluster $\mathcal{DL}$ Set of dataflow path sin the cluster $\mathcal{DP}$ Set of virtual links in the cluster $\mathcal{PL}$ Set of BAG for all VLs $\mathcal{B}^{\circ}$ The initial set of BAG for all VLs $\mathcal{R}^{\circ}$ The initial routing of virtual links $\mathcal{M} = \mathcal{M}^{TT} \cup \mathcal{M}^{RC} \cup \mathcal{M}^{BE}$ Set of all the messages in the cluster $\mathcal{M}^{RC}$ Set of the RC messages in the cluster                                                                                                                                | τς                                                                             |                                                  |

| cluster and can not be removed $ES_i$ An end system $NS_i$ A network switch $E$ Set of physical links $DL$ Set of dataflow links in the cluster $DL^*$ Subset of dataflow links that are fixed in the clus<br>ter and can not be removed $dl_i$ A dataflow link $DP$ Set of dataflow paths in the cluster $dp_i$ A dataflow path $VL$ Set of virtual links in the cluster $vl_i$ A virtual link $BAG(vl_i)$ The BAG of $vl_i$ $B$ The set of BAG for all VLs $\mathcal{R}^{\circ}$ The initial routing of virtual links $\mathcal{M}=\mathcal{M}^{TT}\cup\mathcal{M}^{RC}\cup\mathcal{M}^{BE}$ Set of all the messages in the cluster $\mathcal{M}^{RC}$ Set of the RC messages in the cluster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | E S <sup>SFC</sup>                                                             |                                                  |

| cluster and can not be removed $ES_i$ An end system $NS_i$ A network switch $E$ Set of physical links $DL$ Set of dataflow links in the cluster $DL^*$ Subset of dataflow links that are fixed in the clus<br>ter and can not be removed $dl_i$ A dataflow link $DP$ Set of dataflow paths in the cluster $dp_i$ A dataflow path $VL$ Set of virtual links in the cluster $vl_i$ A virtual link $BAG(vl_i)$ The BAG of $vl_i$ $B$ The set of BAG for all VLs $\mathcal{R}^{\circ}$ The initial routing of virtual links $\mathcal{M}=\mathcal{M}^{TT}\cup\mathcal{M}^{RC}\cup\mathcal{M}^{BE}$ Set of all the messages in the cluster $\mathcal{M}^{RC}$ Set of the RC messages in the cluster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\mathcal{L}S_i$                                                               |                                                  |

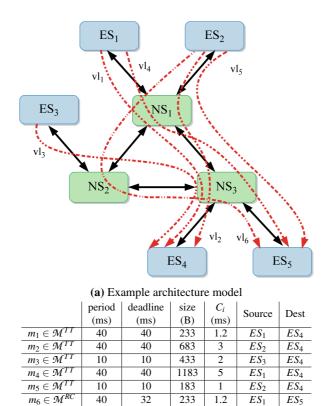

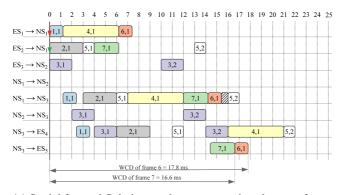

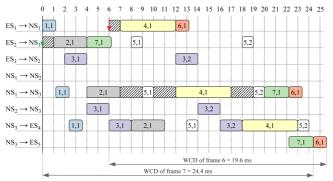

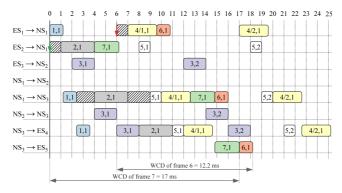

| cluster and can not be removed $ES_i$ An end system $NS_i$ A network switch $E$ Set of physical links $DL$ Set of dataflow links in the cluster $DL^*$ Subset of dataflow links that are fixed in the clus<br>ter and can not be removed $dl_i$ A dataflow link $DP$ Set of dataflow paths in the cluster $dp_i$ A dataflow path $VL$ Set of virtual links in the cluster $vl_i$ A virtual link $BAG(vl_i)$ The BAG of $vl_i$ $B$ The set of BAG for all VLs $\mathcal{R}^{\circ}$ The initial routing of virtual links $\mathcal{M}=\mathcal{M}^{TT}\cup\mathcal{M}^{RC}\cup\mathcal{M}^{BE}$ Set of all the messages in the cluster $\mathcal{M}^{RC}$ Set of the RC messages in the cluster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $2S_i$                                                                         |                                                  |