# Scheduling with Optimized Communication for Time-Triggered Embedded Systems

#### Conditional Process Graph

- Directed, acyclic polar graph with conditional edges used for system representation.

- Each node represents a process assigned to a processing element.

- Conditional edges (in red) have an associated condition. Transmission will take place only if the associated condition is satisfied.

- A process is activated when all its inputs have arrived and issues its outputs when it terminates.

- A process can not be preempted.

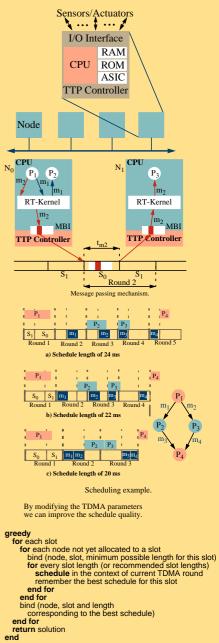

## Time-Triggered Protocol

- TTP was designed for distributed real-time applications that require predictability and reliability.

- The bus access scheme is timedivision multiple-access (TDMA).

- Each node can transmit only during a predetermined time interval, its TDMA slot. A sequence of slots for all nodes is a TDM round. Several rounds can form a cycle that is repeated periodically.

- Every node has a TTP controller.

The TDMA access scheme is imposed by a message descriptor list (MEDL) located in every controller.

- MEDL serves as a schedule table for the TTP controller which knows when to send/receive a message.

| Slot                          |                         |                  |                  |        |

|-------------------------------|-------------------------|------------------|------------------|--------|

|                               |                         | 1.               |                  |        |

| S <sub>0</sub> S <sub>1</sub> | $S_2 \mid S_3 \mid S_0$ | S <sub>1</sub> S | 2 S <sub>3</sub> |        |

| TDMA Ro                       | ound Cual               | e of two ro      | undo "           | Frames |

### Summary

- Scheduling algorithms proposed can be used both for performance estimation and for system synthesis.

- System model capturing both the flow of data and that of control.

- Communication using time-triggered protocol (TTP) implementation.

- Improved schedule quality by considering the overheads of the real-time kernel and communication protocol.

### Hardware Architecture

- Safety-critical distributed embedded systems.

- Nodes connected by a broadcast communication channel.

- Nodes consisting of a TTP controller, a CPU, a RAM, a ROM and an I/O interface to sensors and actuators.

- Communication is based on the TTP.

### Software Architecture

- Real-time kernel on the CPU in each node.

- Local schedule table in each kernel.

- The worst case administrative overheads:

- Ut timer interrupt routine

- $\delta_{PA}$  process activation overhead

- $\delta_{S}$   $\ \ \, sending a message on the same node$

- $\delta_{KS}$  sending a message between nodes

- $\delta_{KR}$  receiving a message from another node

### Problem Formulation

- Input: Safety-critical application modelled by a conditional process graph.

- Mapping of processes to nodes is given.

- Worst case execution delay of a process  $P_i$  is:  $T_P = (\delta_{PA} + t_P + \theta_C + \theta_C) \cdot (1 + U_t)$  where:

$$\boldsymbol{\theta}_{C_1} = \sum_{i=1}^{N_{out}^{local}(P_i)} \boldsymbol{\delta}_{S_i} = \sum_{i=1}^{N_{out}^{remote}(P_i)} \boldsymbol{\delta}_{KS_i} + \sum_{i=1}^{N_{in}^{remote}(P_i)} \boldsymbol{\delta}_{KK_i}$$

Output: Local schedule tables and MEDL, delay (smallest) on the system execution.

### Scheduling Strategy

- Sequence and lengths of the slots in a TDMA round are determined to reduce the delay.

- Previous work extended to handle scheduling of messages within TTP for a given TDMA configuration.

- Two approaches: Greedy heuristic, Simulated Annealing.

- Two variants: Greedy 1 tries all slot lengths, while Greedy 2 uses feedback from the schedule\_message.

- SA parameters are set to guarantee finding near-optimal solutions in a reasonable time.

| No.of<br>proc. |       | ive<br>gner | Greedy 1 |       | Greedy 2 |       |       |       |

|----------------|-------|-------------|----------|-------|----------|-------|-------|-------|

|                | aver. | max.        | aver.    | max.  | time.    | aver. | max.  | time  |

| 80             | 3.16% | 21%         | 0.02%    | 0.5%  | 0.25s    | 1.8%  | 19.7% | 0.04s |

| 160            | 14.4% | 53.4%       | 2.5%     | 9.5%  | 2.07s    | 4.9%  | 26.3% | 0.28s |

| 240            | 37.6% | 110%        | 7.4%     | 24.8% | 0.46s    | 9.3%  | 31.4% | 1.34s |

| 320            | 51.5% | 135%        | 8.5%     | 31.9% | 34.69s   | 12.1% | 37.1% | 4.8s  |

| 400            | 48%   | 135%        | 10.5%    | 32.9% | 56.04s   | 11.8% | 31.6% | 8.2s  |

Percentage deviations of the schedule lengths produced by Greedy 1 and Greedy 2 from the lengths of the near-optimal schedules obtained with the SA algorithm, and the average execution time expressed in seconds.